Shrinking the future: Scientists craft transistors smaller than ever imagined

What's the story

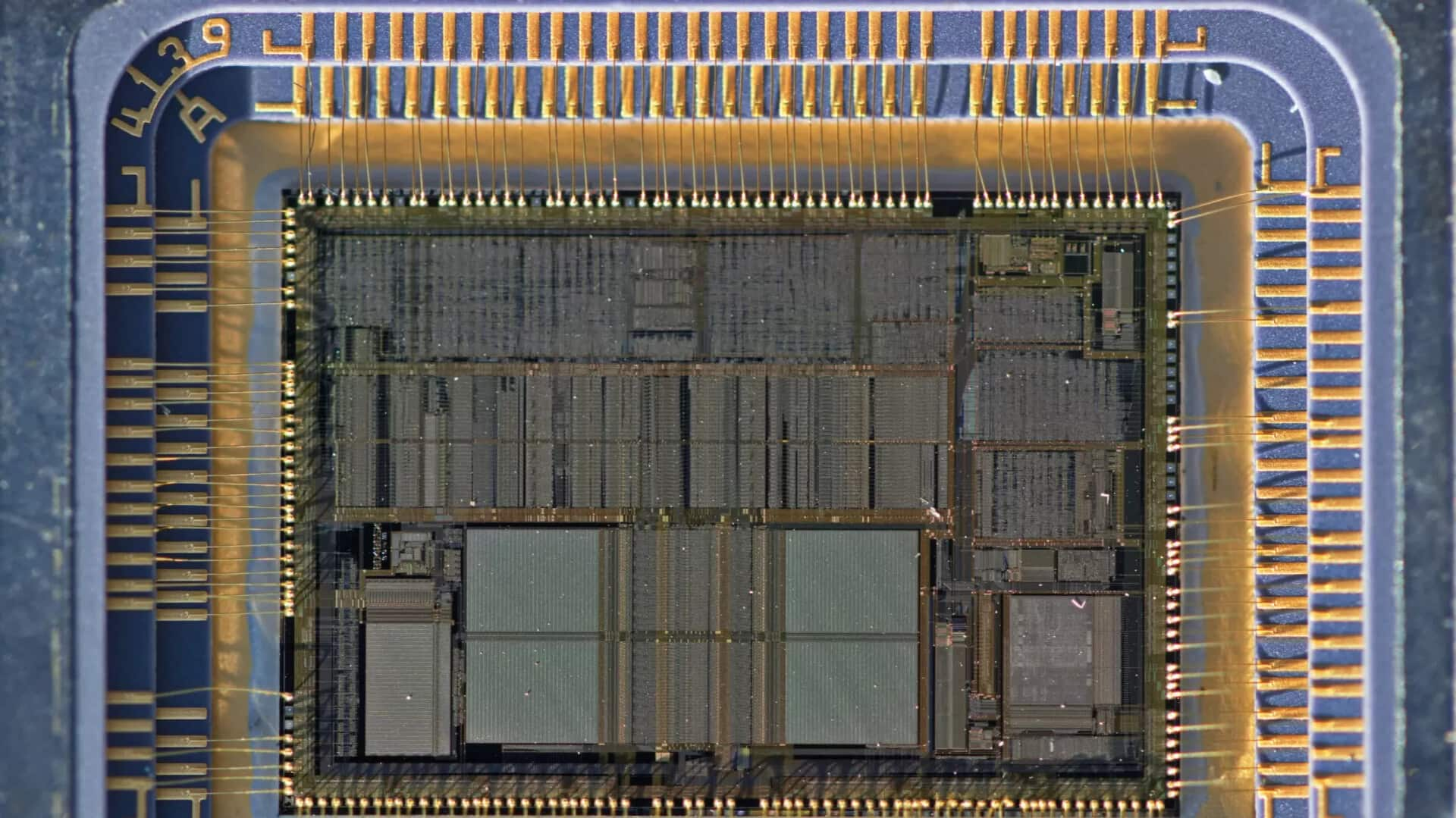

A groundbreaking technique has been developed by a South Korean research team, led by Director Jo Moon-Ho of the Center for Van der Waals Quantum Solids. This innovation could potentially revolutionize semiconductor and nanomaterial technology. The team's method enables the creation of "one-dimensional" metallic nanomaterials with widths as less as 0.4 nanometers, which can be utilized as gate electrodes on 2D substrates.

Manufacturing hurdles

Challenges in 2D semiconductor integration

Two-dimensional semiconductors, despite their excellent electrical properties even at atomic-scale thickness, have posed significant challenges in manufacturing processes for integrated circuits. The integration of these 2D materials into devices sans damaging their delicate structure, has been extremely difficult. Furthermore, achieving consistent large-scale production of high-quality 2D materials has also proven to be a formidable task.

Innovative solution

Overcoming lithography limitations in semiconductor fabrication

Traditional lithography and fabrication techniques have proven inadequate, for the small scales required in 2D semiconductor manufacturing. The research team, led by Jo, has successfully bypassed these limitations by utilizing the mirror twin boundary of molybdenum disulfide. This 2D semiconductor is a 1D metal with a width of just 0.4 nm, and can be used as a gate electrode, thus overcoming the constraints of the lithography process.

Future prospects

New material process for ultra-miniaturized semiconductors

Jo's team has achieved a "1D metallic phase through epitaxial growth," a new material process that can be applied to ultra-miniaturized semiconductor processes. By controlling the crystal structure at the atomic level, they transformed existing 2D semiconductors into a 1D MTB. Jo anticipates this breakthrough to become "a key technology for developing various low-power, high-performance electronic devices in the future."